-

- Contact Us

- Privacy Policy

- term and condition

- Cookies policy

8-1393670-9 Datasheet Guide: Read Specs for RF Design

Designers often discover performance or assembly issues late because connector specs were misread or overlooked; this guide shows how to read a connector datasheet to avoid surprises in RF performance, mechanical fit, and verification. Point: a careful first read of the 8-1393670-9 and the accompanying datasheet prevents costly re-spins. Evidence: common failure modes stem from mismatched impedance and unclear mechanical tolerances. Explanation: invest time up front to map datasheet rows to design checks and test requirements to reach first-pass success.

Why 8-1393670-9 matters in RF designs (background)

Typical RF applications and role in the signal chain

Explain where this connector sits (transmission path, mating interface) and why connector choice impacts insertion loss, return loss, and shielding.

Point: the connector typically sits at the RX/TX interface or on an RF module boundary where it completes the transmission path. Evidence: connector geometry and mating impedance define local discontinuities that show up as insertion loss and S11 reflections. Explanation: designers should treat the connector as a circuit element—its parasitics alter the system S-parameters, create mismatch, and open EMI paths if shields or ground returns are compromised. Diagram suggestion: signal source → cable → connector (mating) → PCB launch → filter → RX.

Key performance risks if specs are ignored

Point: misreading specs creates measurable system failures. Evidence: ignored S-parameter limits or mechanical tolerances lead to higher insertion loss, degraded isolation, and intermodulation products. Explanation: consequences include increased noise figure on receive paths, failed RF acceptance tests, and assembly issues from wrong mating orientation; plan margins and verify mating cycles to avoid these outcomes.

Datasheet structure — sections to prioritize and why (data-analysis)

Header & identification, ordering codes, mechanical drawings

Explain what to confirm immediately: exact part number variant (8-1393670-9), revision/date code, and drawing revision.

Point: identify the exact variant and drawing revision immediately. Evidence: many connector families have near-identical part numbers with different plating, mating gender, or mounting styles. Explanation: confirm revision/date code, ordering code, and the figure that shows mating orientation and pin numbering; highlight that figure in the project repo so mechanical and electrical engineers share the same reference.

Electrical, mechanical, and environmental specification tables

Point: prioritize electrical tables, then mechanical and environmental specifications. Evidence: electrical specs predict RF performance, mechanical specs determine fit and assembly, environmentals set reliability limits. Explanation: map datasheet sections to design checks—electrical → S-parameters and impedance, mechanical → footprint and torque, environmental → operating temp and shock/vibration—to create a simple verification matrix for the project.

Key electrical RF specs — what they mean and how to use them (data-analysis)

Frequency range, characteristic impedance, and S-parameters

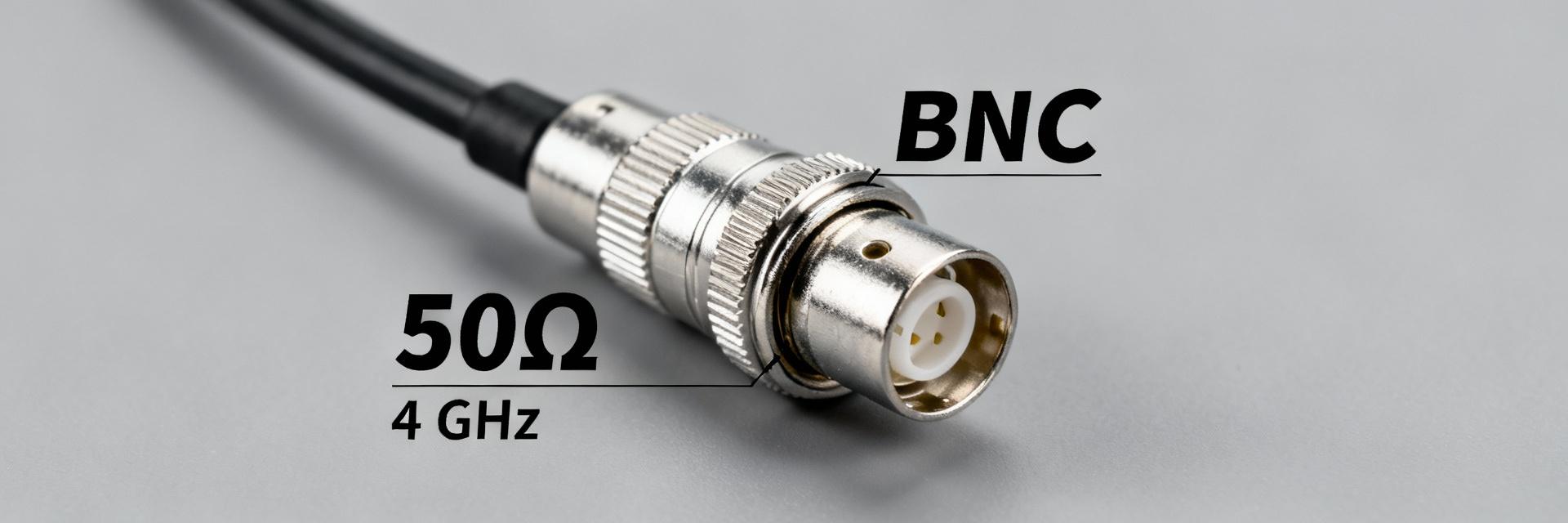

Define each: usable frequency band, specified impedance (usually 50 Ω), insertion loss, return loss/VSWR, and S11/S21 plots.

Point: understand the frequency limits and the format of S-parameter data. Evidence: datasheet tables that list insertion loss and return loss with plotted S-parameters or touchstone files indicate performance vs. frequency. Explanation: trust flat scalar specs only for pass/fail; download or request plotted S-parameter files for simulation, note the reference plane and calibration method used, and validate match to your PCB launch and cable assemblies.

Contact resistance, insulation resistance, and leakage

Point: DC contact specs influence power handling and grounding behavior at low frequency. Evidence: contact resistance and insulation resistance columns show DC limits and isolation thresholds. Explanation: measure contact resistance with 4-wire techniques in the lab, and treat insulation resistance as a proxy for leakage and noise coupling—insufficient insulation can degrade isolation between RF and ground planes.

Mechanical and thermal specs for PCB integration (methods)

Footprint, mounting, torque, and board cutouts

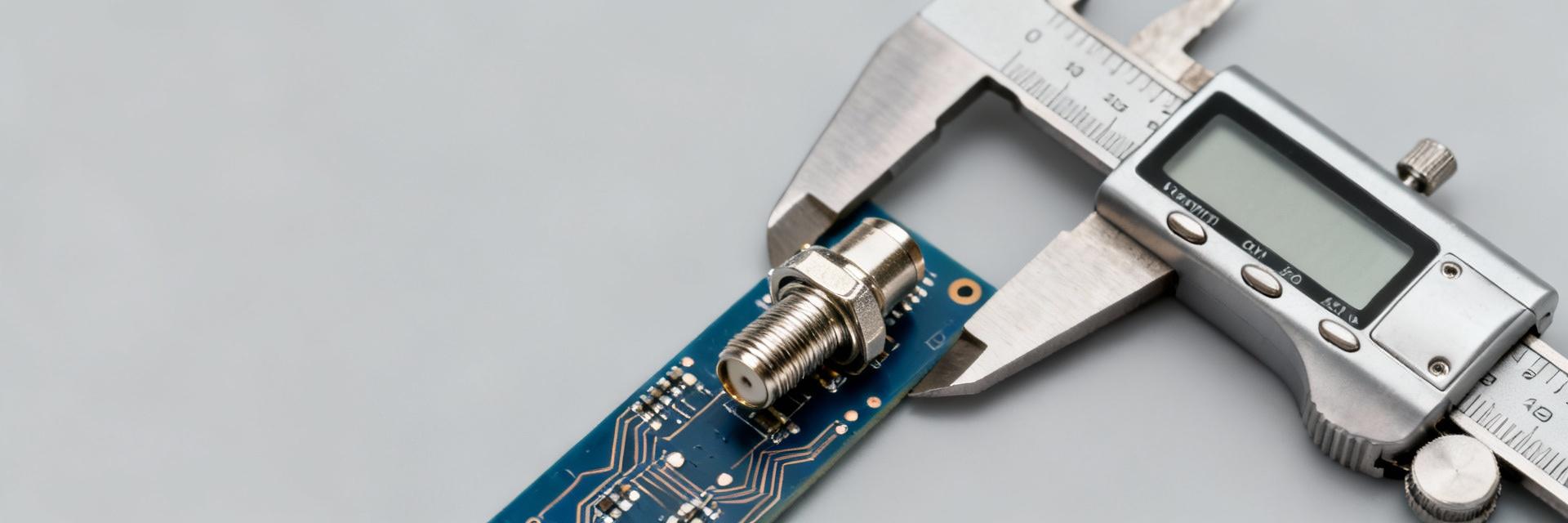

Provide how-to: verify recommended pad layout, keepout, mounting screw torque, and connector height for enclosure clearance.

Point: mechanical compliance prevents assembly failures. Evidence: mechanical drawings list pad sizes, board cutouts, and recommended torque. Explanation: perform a CAD review to confirm pad stack and keepouts, check enclosure clearance for mating/unmating travel, and verify torque values against screw material—capture these checks as sign-offs before sending fabrication files to the PCB vendor.

Materials, plating, and temperature ratings

Point: material and plating affect durability and solderability. Evidence: datasheet notes contact plating (e.g., gold flash, hard gold) and insulator materials plus operating temperature range. Explanation: confirm plating compatibility with your solder profile, check whether conformal coating affects mating, and ensure the operating and storage temperature ratings cover your thermal soak and reflow processes to avoid premature wear or loss of contact integrity.

Interpreting test data and measurement conditions (methods / data-analysis)

Test fixtures, calibration, and reference planes

Explain why test-fixture loss and calibration (SOLT/TRL) matter; require authors to state expected measurement setup to replicate datasheet numbers.

Point: measurement setup defines the meaning of S-parameter curves. Evidence: many datasheets state calibration to connector reference plane or include fixture de-embedding notes. Explanation: replicate expected setup using a VNA with 50 Ω calibration to the connector reference plane, note whether the connector was mated or unmated during measurement, and document fixture contributions to loss so lab results can be compared directly to datasheet curves.

Pass/fail criteria and margin setting

Point: derive production limits from datasheet curves with added margins. Evidence: insertion loss or return loss curves indicate nominal behavior; production variation and fixture loss add uncertainty. Explanation: allocate margin for cable/fixture loss, aging, and temperature drift; create a short checklist for production test limits—VNA sweep tolerance, maximum contact resistance, and a visual/mating inspection pass.

Example integration: a sample RF front-end scenario (case study)

Example: placing 8-1393670-9 on a 50 Ω RX input

Step-by-step: confirm impedance match, layout clearance, and routing rules; select mounting and shielding approach.

Point: practical placement reduces mismatch and EMI. Evidence: layout rules call for controlled impedance lines and nearby ground vias. Explanation: confirm the connector’s characteristic impedance, place ground vias in a stitched fence within 0.08–0.12 in (2–3 mm) of the launch, keep RF traces straight to the connector with short transitions, and add a local shield or chassis connection to control radiated emissions.

Common pitfalls seen in prototypes and how to avoid them

Point: prototypes reveal recurring mistakes. Evidence: common issues include insufficient keepout, wrong torque, and resonance from unsupported overhangs. Explanation: avoid these by enforcing PCB keepouts, using torque-controlled drivers, adding mechanical support for the connector, and running an early RF sweep to spot resonances before volume build.

Practical checklist and implementation steps for designers (action)

Pre-layout checklist

Actionable items: confirm exact part variant (8-1393670-9), get native S-parameter files, import footprint, verify mechanical stack-up.

Point: a concise pre-layout list speeds design reviews. Evidence: missing S-parameters or wrong footprint are leading causes of redesign. Explanation: save a single-source-of-truth spec sheet in the project repo, import manufacturer touchstone files into EM and circuit simulations, and lock the approved footprint and mechanical drawing revision for the layout team.

Post-layout verification and production readiness

Point: post-layout tests validate the build. Evidence: prototype RF sweeps and mechanical cycle tests reveal gaps between theory and real hardware. Explanation: run a VNA sweep against datasheet curves, perform mating/unmating cycle tests, check contact resistance with 4-wire meters, and execute thermal soak and vibration where relevant to confirm production readiness.

Summary

-

Read the key S-parameters and measurement notes on the datasheet and confirm the connector’s reference plane to avoid mismatch and unexpected insertion loss; document this in the project repo to maintain alignment between teams.

-

Prioritize mechanical drawings—verify footprint, mounting torque, and enclosure clearance to prevent assembly failures and ensure robust mating under expected mechanical stress and thermal cycles.

-

Use the pre-layout and post-layout checklists to translate datasheet data into verifiable tests and production limits so the design is validated against real-world conditions for first-pass success with 8-1393670-9.

Common Questions

How should a designer verify S-parameters against their PCB launch?

Point: match reference planes and de-embed fixtures. Evidence: datasheet S21/S11 are only useful if the reference plane aligns with the PCB launch. Explanation: request touchstone files, de-embed fixture loss in simulation, and run a VNA sweep with calibration to the connector plane to confirm insertion and return loss relative to the datasheet.

What mechanical checks are critical before fabrication?

Point: confirm footprint, cutout, and torque. Evidence: mis-sized pads or missing keepouts lead to assembly and reliability issues. Explanation: perform a mechanical CAD review, check screw torque specs on a torque driver, and prototype-fit the connector in the enclosure to validate mating clearance and strain relief.

Which minimal production tests should be run on first articles?

Point: select a compact but effective test set. Evidence: VNA sweep, contact resistance, and mechanical cycle tests identify both RF and assembly failures. Explanation: run a VNA sweep vs. datasheet curves, perform 4-wire contact resistance checks, execute mating/unmating cycles, and document visual inspections to establish baseline production limits.

- Technical Features of PMIC DC-DC Switching Regulator TPS54202DDCR

- STM32F030K6T6: A High-Performance Core Component for Embedded Systems

- APT50GH120B Datasheet Deep Dive: Specs, Ratings & Curves

- APT50GH120BSC20 Power Module: Latest Performance Report

- APT50GH120BD30 IGBT: How to Maximize Efficiency for EV Drive

- GTSM20N065: Latest 650V IGBT Test Report & Metrics

- CMSG120N013MDG Performance Report: Efficiency & Losses

- GTSM40N065D Technical Deep Dive: 650V IGBT + SiC SBD

- NOMC110-410UF SO-16: Live Stock & Price Report

- 1757255 MSTBA 5.08mm PCB: Step-by-Step Install & Solder

-

EXB-V4V120JVPanasonic Electronic ComponentsRES ARRAY 2 RES 12 OHM 0606

EXB-V4V120JVPanasonic Electronic ComponentsRES ARRAY 2 RES 12 OHM 0606 -

EXB-V4V473JVPanasonic Electronic ComponentsRES ARRAY 2 RES 47K OHM 0606

EXB-V4V473JVPanasonic Electronic ComponentsRES ARRAY 2 RES 47K OHM 0606 -

EXB-V4V823JVPanasonic Electronic ComponentsRES ARRAY 2 RES 82K OHM 0606

EXB-V4V823JVPanasonic Electronic ComponentsRES ARRAY 2 RES 82K OHM 0606 -

EXB-V4V151JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150 OHM 0606

EXB-V4V151JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150 OHM 0606 -

EXB-V4V181JVPanasonic Electronic ComponentsRES ARRAY 2 RES 180 OHM 0606

EXB-V4V181JVPanasonic Electronic ComponentsRES ARRAY 2 RES 180 OHM 0606 -

EXB-V4V331JVPanasonic Electronic ComponentsRES ARRAY 2 RES 330 OHM 0606

EXB-V4V331JVPanasonic Electronic ComponentsRES ARRAY 2 RES 330 OHM 0606 -

EXB-V4V152JVPanasonic Electronic ComponentsRES ARRAY 2 RES 1.5K OHM 0606

EXB-V4V152JVPanasonic Electronic ComponentsRES ARRAY 2 RES 1.5K OHM 0606 -

EXB-V4V563JVPanasonic Electronic ComponentsRES ARRAY 2 RES 56K OHM 0606

EXB-V4V563JVPanasonic Electronic ComponentsRES ARRAY 2 RES 56K OHM 0606 -

EXB-V4V104JVPanasonic Electronic ComponentsRES ARRAY 2 RES 100K OHM 0606

EXB-V4V104JVPanasonic Electronic ComponentsRES ARRAY 2 RES 100K OHM 0606 -

EXB-V4V154JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150K OHM 0606

EXB-V4V154JVPanasonic Electronic ComponentsRES ARRAY 2 RES 150K OHM 0606